来源 :概伦电子Primarius2025-06-03

5月27日,2025 “概伦电子技术日”北京站活动成功举办。本次活动以“AI 赋能国产 EDA 新进程”为主题,聚焦AI与EDA技术融合,吸引了集成电路行业专家、高校学者及企业代表齐聚一堂,共同探讨集成电路产业在 AI 时代的变革与发展,为国产EDA技术的创新与应用搭建了高端交流平台。

开篇致辞:锚定AI时代产业发展新机遇

韦承概伦电子副总裁

概伦电子副总裁韦承在欢迎辞中表示,AI技术与EDA的深度融合是国产EDA实现换道超车的关键机遇,需加速技术创新与生态协同。概伦电子将以技术创新为核心,推动AI在EDA领域的落地应用,助力中国集成电路产业高质量发展。

主题演讲:工艺协同,优化设计

逯文忠概伦电子总监

概伦电子总监逯文忠在《工艺协同,优化设计,提升集成电路行业竞争力》主题演讲中提到,概伦电子一直践行DTCO理念,通过EDA创新,应对大规模设计的挑战,打造了业界最领先、最完整的建模解决方案,快速、精准的标准单元库特征化解决方案,持续演进一体化电路仿真验证解决方案。同时,通过业界领先的Design Enablement解决方案不仅支撑晶圆厂的工艺平台研发,更帮助寻求差异化竞争的设计企业建设COT能力,挖掘工艺潜力,优化芯片的YPPAC。

技术前沿:创新路径,为芯片企业打造差异化竞争力

马玉涛概伦电子副总裁

概伦电子副总裁马玉涛在《AI时代模拟和定制电路设计挑战和机遇》的演讲中,从设计场景、工艺协同、效能提升三维度,解析AI技术对EDA工作流的重构路径。当前模拟与定制电路设计仍以晶体管级手动设计为基础,其复杂度随工艺演进持续攀升:先进制程下单个FinFET器件需提取数百个寄生参数,百万级晶体管规模的模拟电路对仿真精度提出更高要求;面向SoC的全芯片设计则需兼顾寄生参数提取(PEX)的效率与容量。EDA工具在精度与速度上,面临双重挑战。概伦电子在AI技术上探索已久,覆盖芯片制造到设计优化全流程,贯穿成熟工艺定制化与先进工艺良率提升,已部署和规划多维度AI/ML融合解决方案。

赵宝磊概伦电子总监

概伦电子总监赵宝磊在《SDEP智能化建模平台,助力缩短工程服务周期》技术演讲中,重点介绍了公司的Spec驱动模型自动化提取平台SDEP?。该平台凭借对业界最新模型的全面支持,在性能和易用性方面实现双重突破,还特别分享了SDEP?在头部客户中的成功应用案例:通过AI驱动的智能参数提取算法,成功将器件建模周期缩短50%;在先进工艺PDK开发中,模型精度也获得显著提升。这一创新成果为半导体行业提供了高效的智能化建模解决方案。

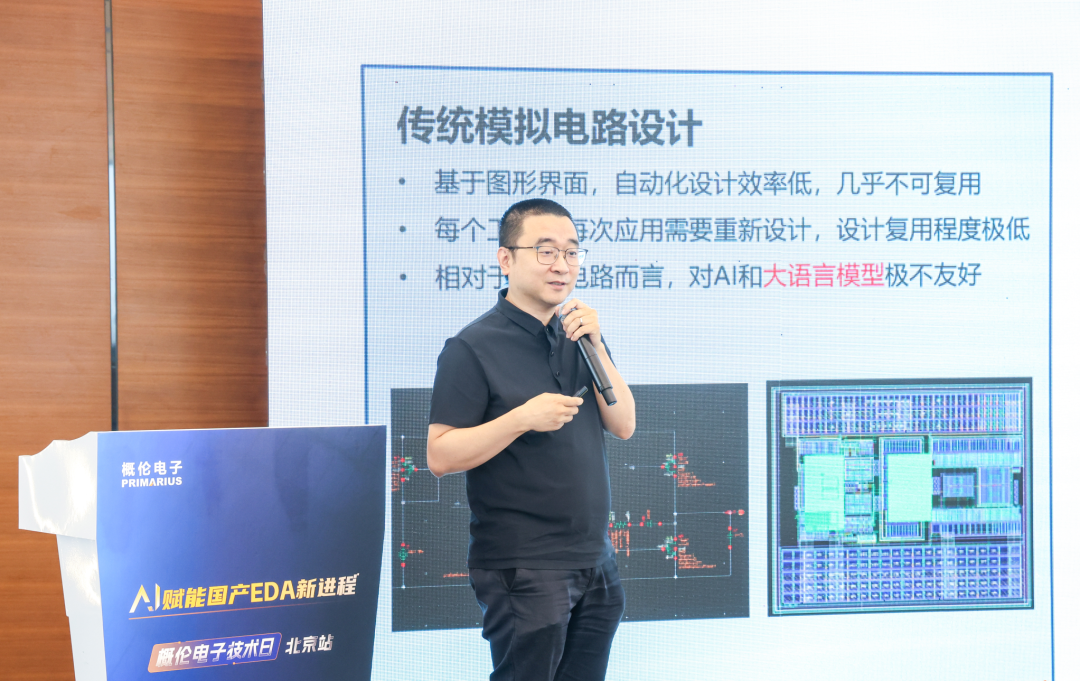

叶佐昌清华大学副教授

清华大学副教授叶佐昌在《AI赋能的模拟电路设计》主题演讲中,系统性地阐述了模拟电路设计的创新方法论。他首先开创性地提出了"代码化模拟电路设计"的全新理念,随后重点展示了其团队研发的TED工具平台及其核心技术突破。最后,叶教授前瞻性地分享了多个AI技术赋能模拟电路自动化设计的创新研究方向,为行业提供了具有实践价值的智能化解决方案。

邓雨春概伦电子高级总监

概伦电子高级总监邓雨春在《持续创新,高效快速仿真应对高性能芯片应用挑战》技术演讲中,详细介绍了概伦电子NanoSpice家族仿真解决方案。该方案以2倍以上的仿真速度优势,为高性能芯片设计提供一站式支持:其中True SPICE工具NanoSpice X?实现了从器件模型、模块级电路到高精度模拟全芯片仿真的全流程覆盖;FastSPICE工具NanoSpice Pro X?则专注于SoC、存储器电路和CLK tree等复杂场景的高效仿真。他还特别强调,通过NanoSpice?与数字仿真器VeriSim?的混仿技术,配合完整的模型支持体系,该方案已构建起覆盖各类仿真和验证方法学的完整技术生态。目前,这项经过国际国内头部芯片公司十余年验证的成熟技术,已全面支持SPICE、FastSPICE和CoSim等多种仿真模式,为芯片设计行业提供了可靠的高性能仿真解决方案。